Western Digital Technologies, Inc. or its affiliates' (collectively "Western Digital") general policy does not recommend the use of its products in life support applications where in a failure or malfunction of the product may directly threaten life or injury. Per Western Digital Terms and Conditions of Sale, the user of Western Digital products in life support applications assumes all risk of such use and indemnifies Western Digital against all damages.

This document is for information use only and is subject to change without prior notice. Western Digital assumes no responsibility for any errors that may appear in this document, nor for incidental or consequential damages resulting from the furnishing, performance or use of this material.

Absent a written agreement signed by Western Digital or its authorized representative to the contrary, Western Digital explicitly disclaims any express and implied warranties and indemnities of any kind that may, or could, be associated with this document and related material, and any user of this document or related material agrees to such disclaimer as a precondition to receipt and usage hereof.

Each user of this document or any product referred to herein expressly waives all guaranties and warranties of any kind associated with this document any related materials or such product, whether expressed or implied, including without limitation, any implied warranty of merchantability or fitness for a particular purpose or non-infringement. Each user of this document or any product referred to herein also expressly agrees Western Digital shall not be liable for any incidental, punitive, indirect, special, or consequential damages, including without limitation physical injury or death, property damage, lost data, loss of profits or costs of procurement of substitute goods, technology, or services, arising out of or related to this document, any related materials or any product referred to herein, regardless of whether such damages are based on tort, warranty, contract, or any other legal theory, even if advised of the possibility of such damages.

This document and its contents, including diagrams, schematics, methodology, work product, and intellectual property rights described in, associated with, or implied by this document, are the sole and exclusive property of Western Digital. No intellectual property license, express or implied, is granted by Western Digital associated with the document recipient's receipt, access and/or use of this document or the products referred to herein; Western Digital retains all rights hereto.

This document and Western Digital communications to the user associated therewith, shall be treated as Western Digital Corporation's proprietary and confidential information, protected by the recipient as such, and used by the recipient only for the purpose authorized in writing by Western Digital Corporation. This document shall be covered as Western Digital Corporation's confidential information under all applicable nondisclosure agreements between the recipient and Western Digital Corporation.

Western Digital and the Western Digital logo are registered trademarks or trademarks of Western Digital Corporation or its affiliates in the U.S. and/or other countries. The microSD, microSDHC, microSDXC and SD marks and logos are trademarks of SD-3C, LLC. All other marks are the property of their respective owners. Product specifications subject to change without notice. Pictures shown may vary from actual products. Not all products are available in all regions of the world.

© 2018 Western Digital Corporation or its affiliates. All rights reserved.

#### Table of Contents

## TABLE OF CONTENTS

| 1. | INT                              | Introduction                            |       |  |  |

|----|----------------------------------|-----------------------------------------|-------|--|--|

| 2. | BRIEF BACKGROUND ON FLASH MEMORY |                                         |       |  |  |

| 3. | WH                               | HY MANAGED NAND?                        | ····· |  |  |

| 4. | Col                              | NSIDERATIONS IN USING SD & E.MMC        | 8     |  |  |

|    |                                  | Performance                             |       |  |  |

|    | 4.2                              | Write Amplification and Write Endurance |       |  |  |

|    | 4.3                              | Read Endurance                          |       |  |  |

|    | 4.4                              | Data Retention                          | 10    |  |  |

|    | 4.5                              | High Reliability Applications           | 10    |  |  |

|    |                                  | Operation Time Out                      |       |  |  |

|    | 4.7                              | Power Immunity                          | 10    |  |  |

|    |                                  | Layout Considerations                   |       |  |  |

|    | 4.9                              | Programming                             | 1     |  |  |

| 5. | SUN                              | MARY                                    | 11    |  |  |

## List of Figures

| Figure 3-1 | Raw NAND vs  | Managed NAND    | Solutions   | 8 |  |

|------------|--------------|-----------------|-------------|---|--|

| 11901651   | Naw Name vs. | Tidilagea NAIND | 3010110113. |   |  |

#### List of Tables

# LIST OF TABLES

| Table 2-1 | Memory Management Techniques          | .7 |

|-----------|---------------------------------------|----|

| Table 4-1 | Example of Write Amplification Impact | 9  |

#### 1.0 Introduction

This paper gives a brief history of managed NAND flash memory and discusses some of the key considerations when designing with today's high performance SD cards and e.MMC devices.

#### 2.0 Brief Background on Flash Memory

Flash memory was productized in the late 1980's as a replacement for EPROM. Flash memory was erasable and re-programmable in system and offered higher densities and lower costs versus EPROM. The most common type of early Flash memory was called "NOR" flash – which allowed for random read and write access to any address. The introduction of NAND flash memory allowed for a more dense array (translating to lower costs), but was only accessible a page at a time – this was ideal for storage applications, but not efficient for direct code execution (code had to be loaded in RAM one page at a time for the CPU to execute from). NAND flash memory quickly became the de-facto standard for high-density solid state storage.

The nature of NAND flash memory requires that before programming (or writing), it has to be erased a "block" at a time – which means the host had to manage the data in the blocks and move it around as needed to free up space. As flash memory blocks are programmed and erased, the cells "wear" out to the point where data can no longer be reliably retained. Flash memory file systems were developed to manage program and erase operations and to extend the life of the memory by techniques such as wear leveling, error-correcting code (ECC), and bad block management.

Table 2-1. Memory Management Techniques

| Memory Management<br>Technique | Benefit                                                                                               |

|--------------------------------|-------------------------------------------------------------------------------------------------------|

| Wear Leveling                  | Move data from frequently erased blocks to less accessed blocks to even out the "wear" on the memory. |

| ECC                            | Detect and correct data errors during reads.                                                          |

| Bad Block Management           | Retire "bad" blocks from a pool of spare blocks in the memory.                                        |

# 3.0 WHY MANAGED NAND?

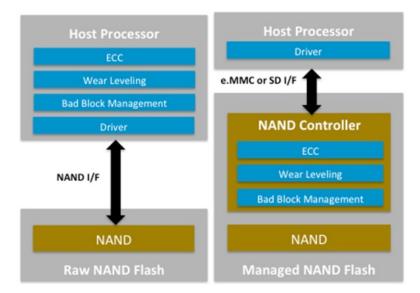

If you are using "raw" NAND memory, your own host controller has to manage ECC and other flash memory management functions. Memory devices like SD cards and e.MMC flash drives included these management functions on the device – so the memory could be used like traditional storage devices. Internal to the device is a small controller, firmware, and one or more stacked NAND die. The host (SOC – system on chip) controller simply needed an interface to the SD or e.MMC bus, a file system and drivers optimized for the card characteristics.

Figure 3-1. Raw NAND vs. Managed NAND Solutions

As NAND memory became higher density and cell size shrunk, more and more sophisticated ECC and management techniques were required. For most SOC designers, it became easier to off-load the NAND management to a controller coupled to the memory. SD cards offered limited performance for the main OS and applications in multi core/GHz CPUs – so the e.MMC interface became a JEDEC standard way of interfacing to on-board managed NAND. Today's e.MMC 5.0 interface runs at speeds of up to 400MB/sec.

# 4.0 Considerations in Using SD & E.MMC

While the interfaces have been standardized, there are enough differences between the internal operations of different managed memory "devices", and the host needs to consider these for optimized system level performance and life.

## 4.1 Performance

The primary differences that users will see between devices relate to performance and "wear" life. There are multiple types of NAND flash memory that may be used internally to the device, for example 2-bit (MLC) and 3-bit (TLC) per cell flash memory. Many devices may also be configured with SLC areas or caches, and multiple memory devices or "planes" of memory may be accessed in parallel for higher performance. Latencies for read or write operations will differ between devices, and need to be taken into consideration on the host side (for example if you are continuously recording a data stream, you need to be able to buffer enough of that stream on the host side in RAM to account for the worst case write latency on the managed NAND device). For SD cards, "Speed Class" refers to the "minimum" sustained write speed under a specific SDA defined write pattern; a detailed description of this write pattern is available to SDA members in the SD specifications. If your write pattern significantly differs from the SDA spec, you may observe significantly different performance. Maximum write speeds are also specified in data sheets for SD cards and e.MMC devices – but this will also be dependent on the host side implementation.

# 4.2 Write Amplification and Write Endurance

Another key consideration is "write amplification". When the host writes a page or "pages" to the memory device – internal operations inside the managed NAND device will cause additional writes to occur to the memory (management overhead). Large sequential writes aligned to page boundaries typically result in the least "amplification" (In a well designed system this amplification factor could be ~1.1). Small random writes typically result in the most amplification (in a bad design, the factor could be >2.0). This becomes important when considering the life of the memory device. See the example below:

Table 4-1. Example of Write Amplification Impact

| Item                                     | Value                   |

|------------------------------------------|-------------------------|

| Device Capacity                          | 8GB                     |

| Write Endurance                          | 2K Program/Erase cycles |

| Data Written Per Day to Device           | 2GB                     |

| Expected Life w/ WA=1<br>=(8x2000)/(2*1) | 8,000 days              |

| Expected Life w/ WA=5<br>=(8x2000)/(2*5) | 1,600 days              |

To estimate the write amplification for any particular device, and hence its expected life, you can capture a log file of your writes. In some cases you may find that a TLC product rated at a fraction of the write life will be sufficient in your design and be a way to reduce cost. Because of SLC caching and other management techniques, vendors are moving away from a pure cycle rating to a terabyte written (TBW) rating on newer devices, which can better reflect the devices true capability.

#### 4.3 Read Endurance

As memory cells get closer together, reading one cell can disturb the data in surrounding cells. If the same cell is read enough times, data from surrounding cells may not be readable anymore, resulting in a UECC (uncorrectable ECC). For many applications, this will not be a critical consideration, since writing the device will trigger wear leveling, which will move the least used data, by re-writing it somewhere else in memory, and thus "refreshing" the cells. However in applications that rarely write data to the device, but are constantly reading the same areas, host side refresh techniques maybe required to ensure you do not reach the readendurance limits. If this is a concern, you should discuss your access patterns with your memory vendor's applications engineering team to better understand this phenomenon. The simplest refresh technique is to just cycle through the memory periodically and read and rewrite each page of data.

#### 4.4 Data Retention

Data retention changes with temperature and cycle life of the memory device. JEDEC specifies 10 years @ 550C data retention for a fresh device (typically that means it has not been erased or programmed more than 10% of its rated cycle life). Data retention is not linear with temperature. The first step to understand if data retention is a consideration in the device is to create a worst case daily temperature profile for you application. The memory vendor should then be able to help you calculate expected life. Life can be easily extended by "refreshing the data" – e.g., re-writing the data back to a different memory location, and in some cases it may be recommended that the host triggers such a function periodically (again if you are writing enough data to the device, the standard wear leveling mechanisms should take care of this for you – so it is of most concern in low write environments).

# 4.5 High Reliability Applications

For most standard applications, a UECC rate of 1x10^15 reads or so may be acceptable. Depending on the type of data that is lost, the host may still be able to recover (e.g., reboot) and reload the data. A journaled file system may also be used for better protection. The most critical areas of data typically include the internal flash memory management tables, boot partition and the host OS kernel. Memory vendors may keep backup copies of internal flash memory management tables to enable recovery in the event of a UECC read. In addition, boot partitions are typically kept in SLC areas with a redundant copy for extra reliability. A backup copy of the host OS kernel and other critical data structures may be kept in the user area to allow for additional redundancy – that would typically be managed by the OS vendor.

# 4.6 Operation Time Out

During a read or write operation to the flash memory, the operation may timeout; this typically happens if the host driver is not following the maximum timeout recommendations for read and write operations. The host needs to consider error handling on a timeout, and retry the operation as necessary.

# 4.7 Power Immunity

The host design needs to consider the effect of power loss during flash memory operation. Many e.MMC and some SD card products will be resilient to some degree if power is interrupted to the memory during an erase or write operation. The host should be able to recover from power loss during READ, simply by resetting the flash memory device and starting the read again (or in a worst case, by rebooting). In the case of a write operation, if the host still has the data, the write can be attempted again. The worst case scenario is typically power loss during an internal "housekeeping" operation in the flash memory. If an internal management table or pointer is corrupted, this can lead to unrecoverable data scenarios. Power immunity hardware and software may protect against this to varying degrees – but good host side power supply design is the key to maximizing robustness (such as sufficient power supply capacitance and avoiding rapid power cycling).

#### 4.8 Layout Considerations

As e.MMC devices operate on a high speed bus, host designers should follow the vendors recommendations on signal layout. Routing may be possible through NC balls on the BGA to minimize the number of board layers and vias– again the host designer should check with the vendor for specific layout guidelines.

SD cards can also operate in a number of interface modes. The SDA provides documentation with recommendations on how to design with this interface and that should be studied carefully – especially when using the higher speed UHS-104 and UHS-II buses.

## 4.9 Programming

Many e.MMC devices are typically pre-programmed before surface mount (SMT) – however as NAND geometries shrink, careful consideration maybe required as to how the device is pre-programmed and in some cases, data may need to be loaded or checked on the host board (after SMT). Again, check with you flash memory vendor for recommended practices for the specific device you are using.

## 5.0 SUMMARY

NAND flash memory is a complex technology and is becoming more and more complex with each geometry shrink. Its intrinsic challenges require sophisticated flash management techniques. When designing with today's high performance SD cards and e.MMC devices, taking into consideration the key topics discussed in this paper will help to optimize system level performance and product life.

# Western Digital.

For service and literature:

support.wdc.com

www.wdc.com

800.ASK.4WDC North America

+800.6008.6008 Asia Pacific

00800.ASK.4WDEU Europe (toll free where available)

+31.88.0062100 Europe/Middle East/Africa

Western Digital 5601 Great Oaks Parkway San Jose, CA 95119 U.S.A.

August 2018