## Essential Mechanical Innovations to Drive Industry Leading Capacities

Prepared by: Western Digital TECHNICAL BRIEF Western Digital.

A hard disk drive (HDD) is an incredibly complex piece of hardware and software. It has nearly 300 components, from hundreds of suppliers worldwide. It requires high-precision manufacturing—many of the design parameters have tolerances of less than 1nm. It has more than a million lines of software code to conduct host communications, mechanical operations and data recording.

Western Digital continuously invests in R&D to achieve the highest capacity HDDs. Aeronautical, mechanical, electrical and chemical engineering, material science, signal processing and code theory engineering, along with computer engineering are just some of the many technology disciplines required to build modern HDDs.

Western Digital's latest generation Ultrastar\* DC HC550 18TB¹ CMR HDD and Ultrastar DC HC650 20TB SMR HDD are industry leaders for high capacity data center HDDs. Higher capacities enable lower Total Cost of Ownership (TCO) for data centers, enabling the exponential growth of worldwide data.

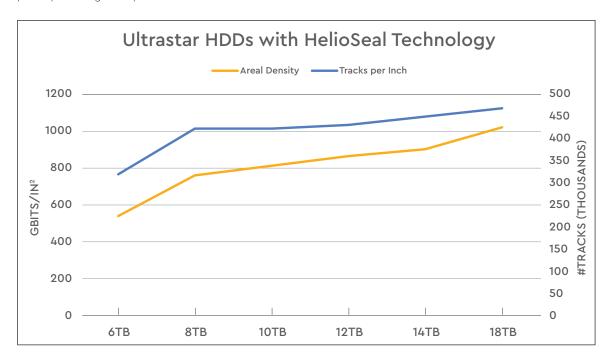

Higher Tracks Per Inch (TPI) and growth in areal density, the measure of how much data can fit onto an HDD platter, drive higher capacities and are a result of continuous HDD innovation.

TECHNICAL BRIEF Western Digital.

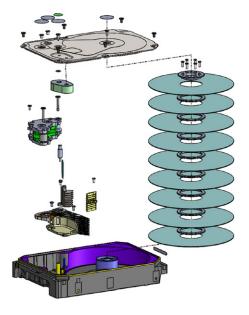

New mechanical innovations to increase TPI and areal density include an industry-first Triple Stage Actuator (TSA), improvements to the spindle motor, and an all-new, 9-disk mechanical platform with even thinner components. These all work together with the industry's first Energy Assist Magnetic Recording (EAMR) technology and proven HelioSeal\* technology, as well as Shingled Magnetic Recording (SMR) technology for the 20TB capacity, to achieve industry-leading capacity products.

## **Triple Stage Actuator**

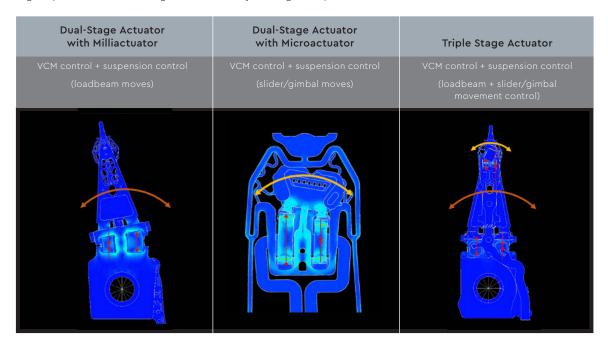

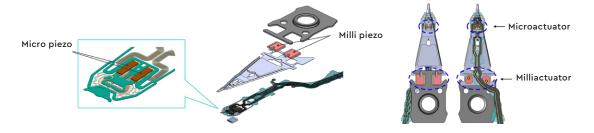

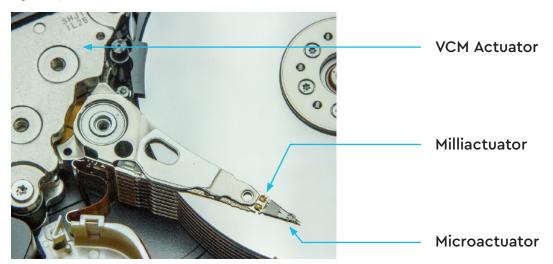

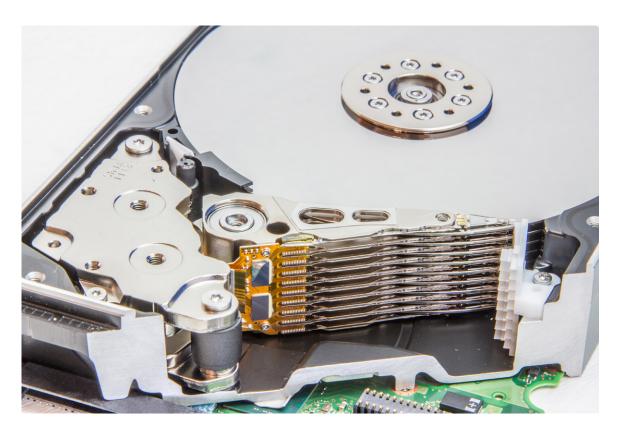

Actuator technology has evolved from single stage to dual stage to triple stage actuators. Each evolution increases the read-write head position accuracy while decreasing the amount of time required to read and write the media. The first dual-stage actuators used the milliactuator to move the loadbeam. The next generation of dual stage actuators replaced the milliactuator with a microactuator. The Ultrastar DC HC550/HC650 are the industry's first HDDs to combine field-proven milliactuator and microactuator technologies into a triple stage actuator, creating three independent pivots that more precisely position the head over the data track. This higher precision results in higher areal density and higher capacities.

A TSA makes use of three pivot points: The Voice Coil Motor (VCM) Actuator, the milliactuator and the microactuator. The milliactuator and microactuator each has a pair of piezoelectric elements (or "piezo elements") attached to the different components of the suspension. The actuator rotates when a voltage is applied, causing one piezo element to expand while the opposite piezo element contracts.

The milliactuator can pivot up to 200nm while the microactuator can pivot up to 100nm. The TSA with three pivot points can increase granularity during track following and seeking.

During track following the actuator stays on a particular data track to read/write data. The TSA decreases head position error to help mitigate the effect of vibrations from the internal spinning disks, seek-induced vibrations, as well as external system vibrations. This allows for more precise positioning of the head on the track.

During seek the actuator arm is moving from one track to another. As the arm approaches the target track, the milliactuator/microactuator are turned on in order to align to the target track faster. Finer positioning control enables the ability to arrive on-track more quickly, while reducing ringing and vibration.

These improvements in precision and performance enable higher TPI, with track width for the Ultrastar DC HC550/650 at ~50nm. Higher TPI leads to higher areal density, which allows for more data on each disk and higher capacities.

## 9-Disk Platform and Component Design

The Ultrastar DC HC550/HC650 use Western Digital's first 9-disk platform and are industry leaders for areal density at 1022/1160 Gbits/in², respectively. A number of optimizations were made to increase platters and improve power consumption efficiency in the same 3.5" form factor as prior generations.

The spindle motor was re-designed with the objective to increase idle power consumption efficiency. This was accomplished by optimizing the electromagnetic design for the spindle motor while reducing bearing friction.

|                                                     | Ultrastar DC<br>HC530, 14TB | Ultrastar DC<br>HC550, 18TB |

|-----------------------------------------------------|-----------------------------|-----------------------------|

| Power consumption at idle (W/TB), SATA <sup>2</sup> | 0.39                        | 0.31                        |

The thickness of several components was reduced compared to the prior generation. The thickness of the PCBA board was reduced by up to 42%. Other components that were slimmed include the top cover, the media disk, the disk spacer and the actuator arm.

## **Summary**

The Ultrastar DC HC550 18TB CMR HDD and DC HC650 20TB SMR HDD make use of several mechanical innovations to enable industry-leading capacities of 18TB and 20TB, respectively. Western Digital continues to be a leader in actuator technology, introducing a triple stage actuator for greater accuracy, allowing for higher TPI and thus greater areal density. Thinner components have been engineered to fit 9-disks within a standard 3.5" form factor. These mechanical innovations, together with EAMR and proven HelioSeal technology, enable data centers to lower TCO while maintaining workload reliability and performance.

<sup>&</sup>lt;sup>1</sup>One terabyte (TB) is equal to one trillion bytes. Actual user capacity may be less due to operating environment.

<sup>&</sup>lt;sup>2</sup> Idle specification is based on use of Idle\_A